锐杰微科技携Chiplet全流程解决方案精彩亮相第八届中国系统级封装大会

2024年8月27日-29日,elexcon2024深圳国际电子展暨 SiP China 2024第八届中国系统级封装大会在深圳福田会展中心盛大开幕。锐杰微科技作为聚焦Chiplet&高端芯片的OSAT企业精彩亮相本次大会。

8月28日上午,锐杰微科技集团董事长方家恩先生在第八届系统级封装大会分论坛三发表异构系统集成实现(生态圈)发表《Chiplet芯片技术在封装级的相关应用》的主题演讲。

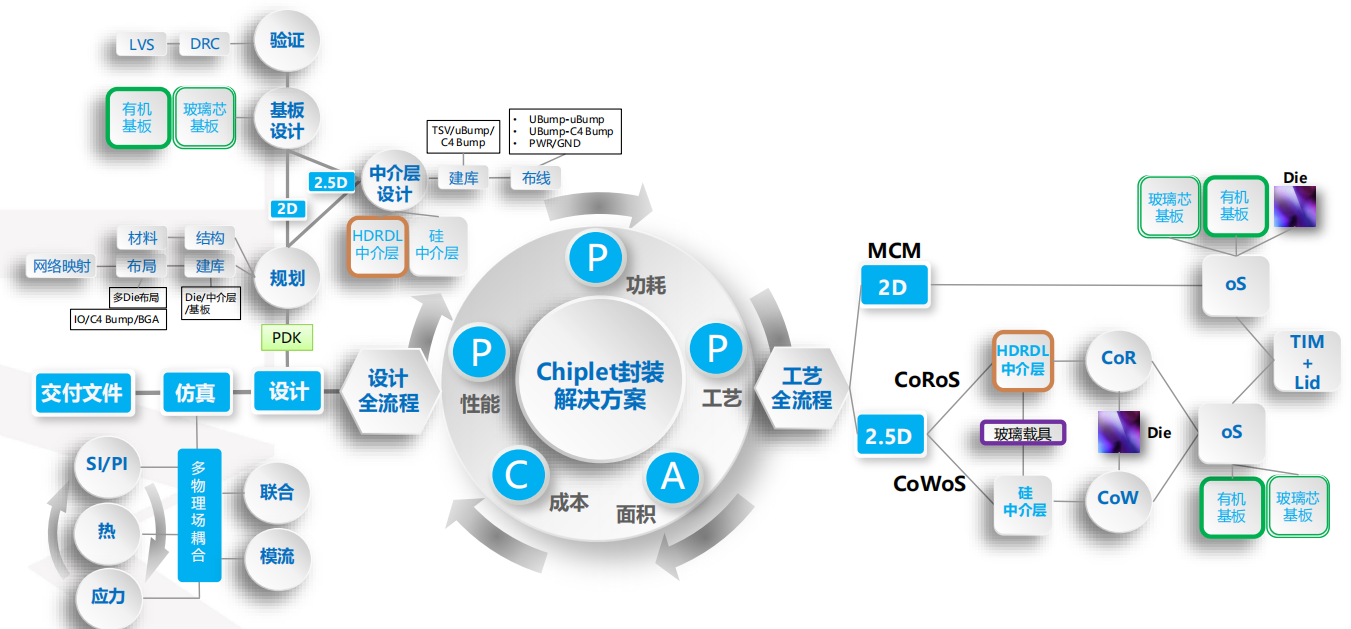

从数据中心到AI革命,AI算力需求激增需求推动了高端芯片持续发展,先进封装技术(Chiplet)迎来了难得发展机遇。方家恩先生在主题演讲中阐述了Chiplet集成芯片的产业观点,围绕封装技术路线、芯粒互联的封装设计和组装工艺平台的重要节点,分享锐杰微科技在封装级的应用实践。

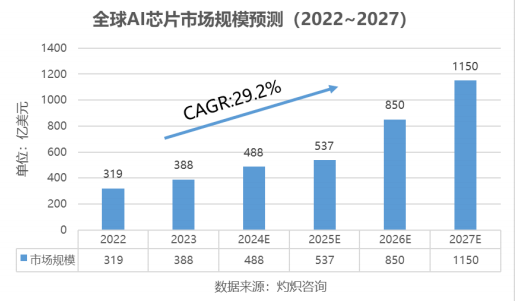

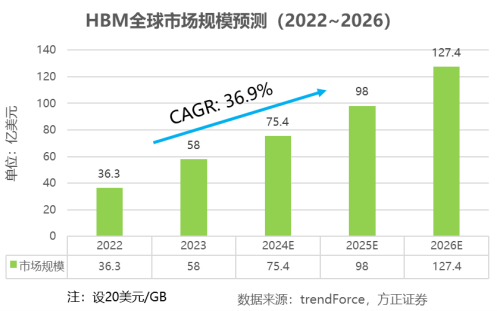

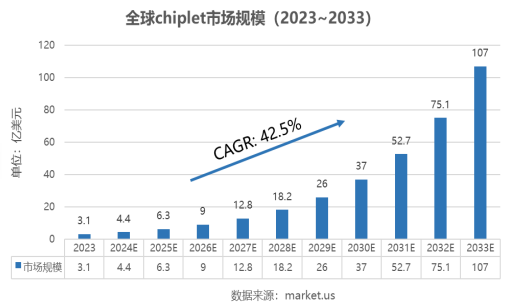

算力、算法和数据是推动人工智能发展的核心要素。根据分析机构预测:2024~2029年,中国人工智能市场规模,将从6600亿人民币达到近1.1万亿人民币,年复合增长率达到7.2%;2022~2027年,全球AI芯片市场规模,从319亿美元将达到1150亿美元,年复合增长率达到29.2%;HBM芯片市场规模,从36.3亿美元将达到127.4亿美元,年复合增长率达到36.9%;2023~2033年,Chiplet芯片市场规模,从3.1亿美元将达到107亿美元,年复合增长率达到42.5%。

高算力、高带宽、低延时和低功耗/bit是高端芯片追求的关键技术指标,超大规模芯片广泛采用Chiplet技术已经成为趋势。Nvidia(B200),AMD(MI300x),Intel(Intel Sapphire Rapids)等采用基于D2D互联的2.5D/3D先进封装形式。层间互联技术和2.5D & 3D CoW/CoS装配工艺技术是锐杰微的重要研究方向。目前,锐杰微已在Chiplet D2D 高速互联封装技术、2.5D CoW装配工艺验证、国产HBM封装方案、基于2D MCM封装技术的超大尺寸、大功率、高密度I/O超算芯片、UCIe1.0标准 x32 24Gbps D2D性能验证、面向设计全流程和工艺全流程的封装工艺平台搭建、行业标准制定方面做了多方位实践。下一步,锐杰微将结合局部硅互联和RDL中介层,利用两者的优点以实现高密度die-to-die互联,更灵活的信号传输和成本效益。

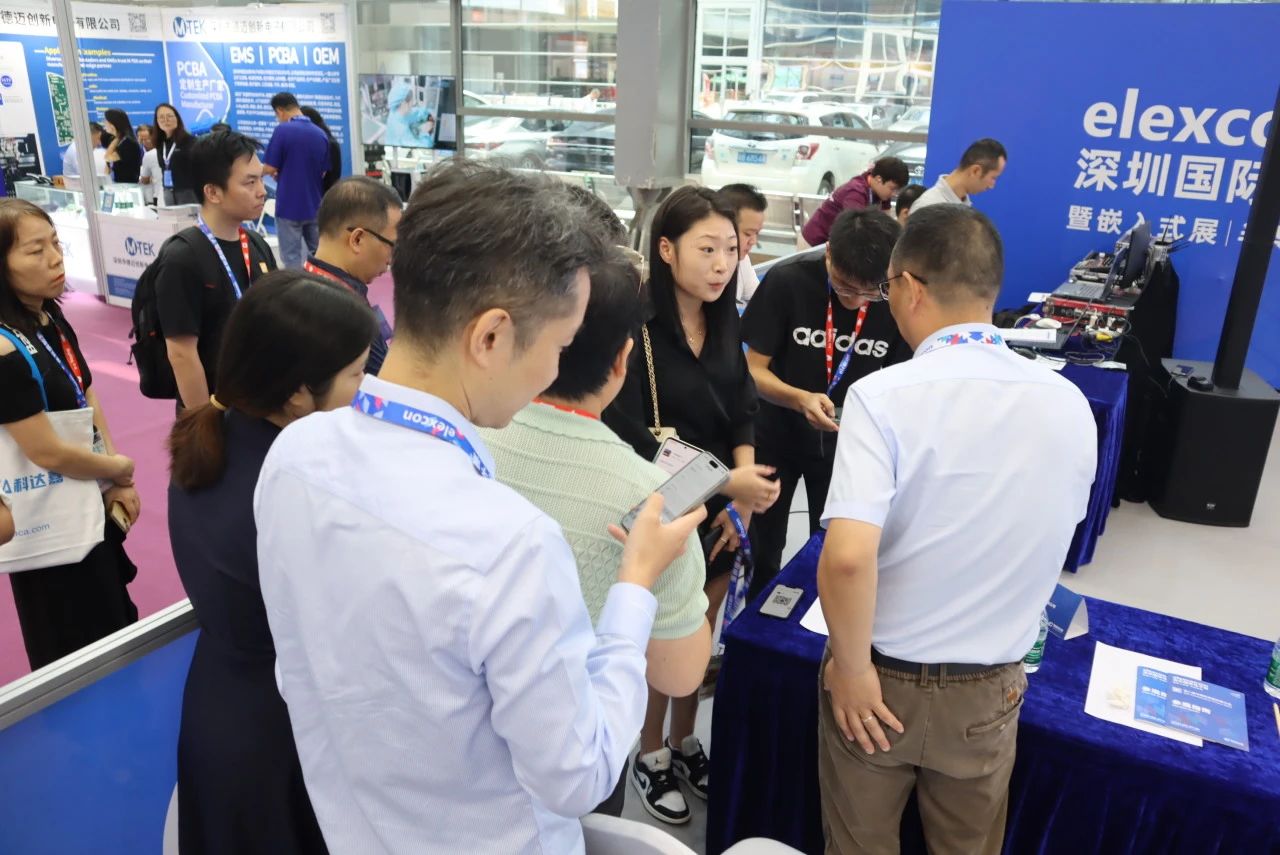

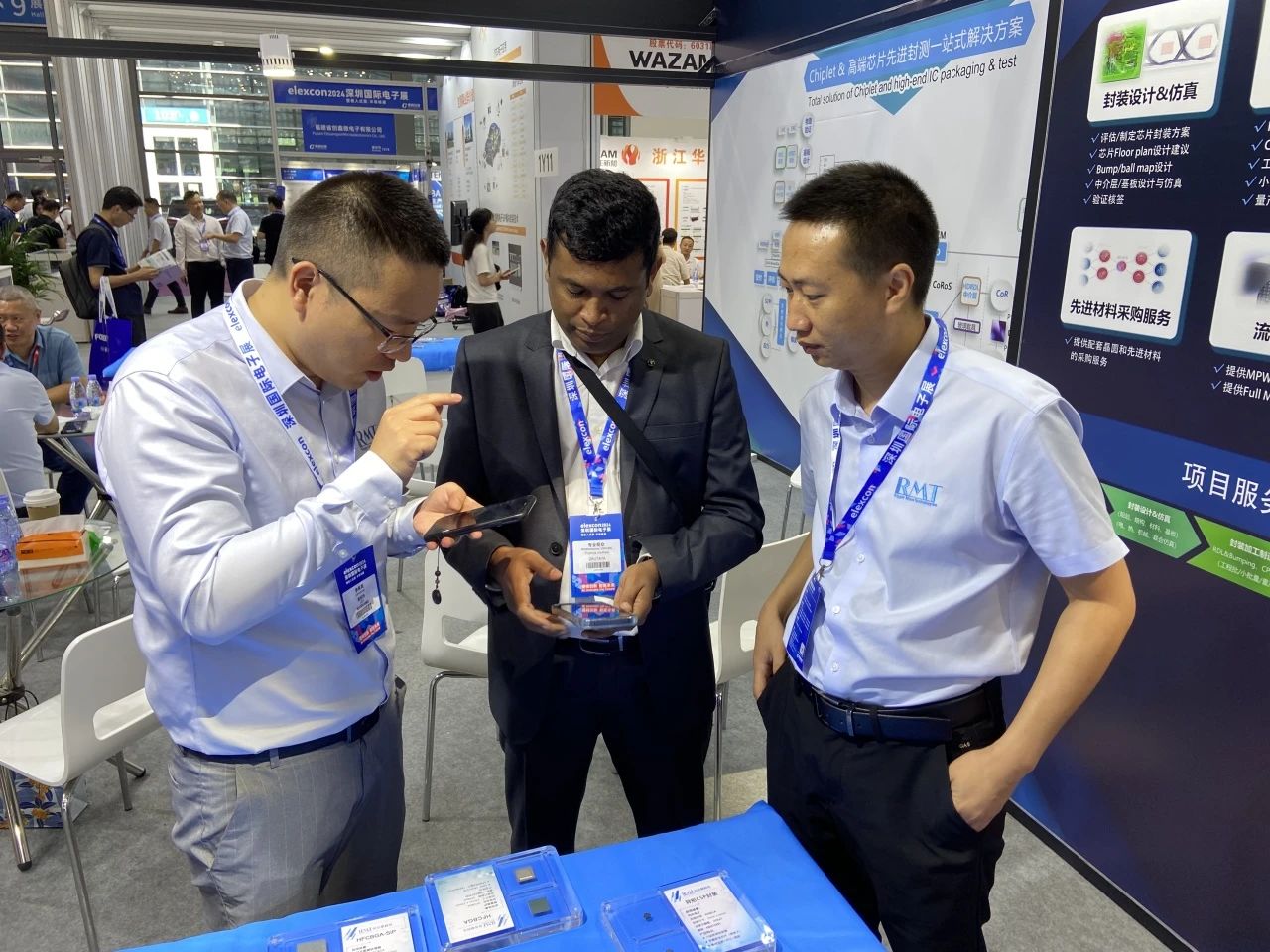

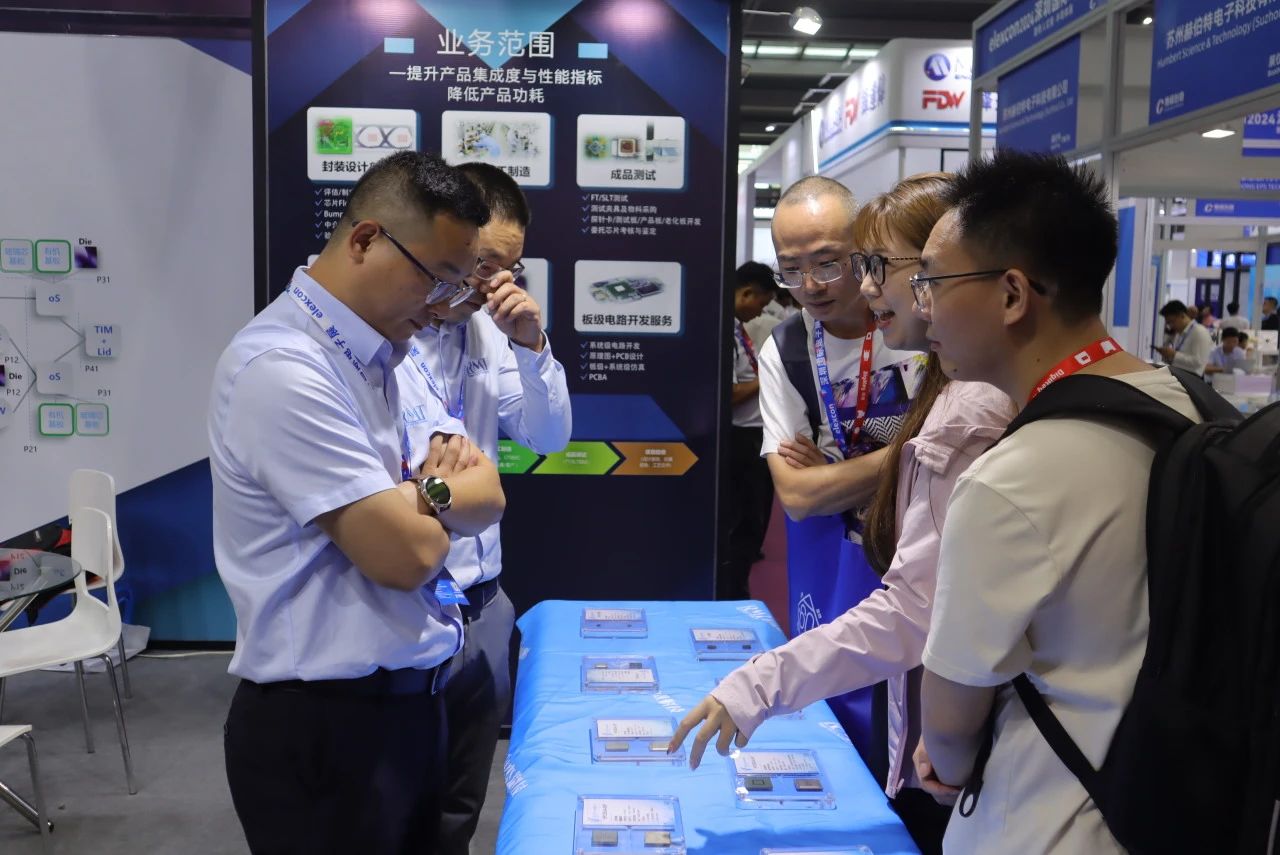

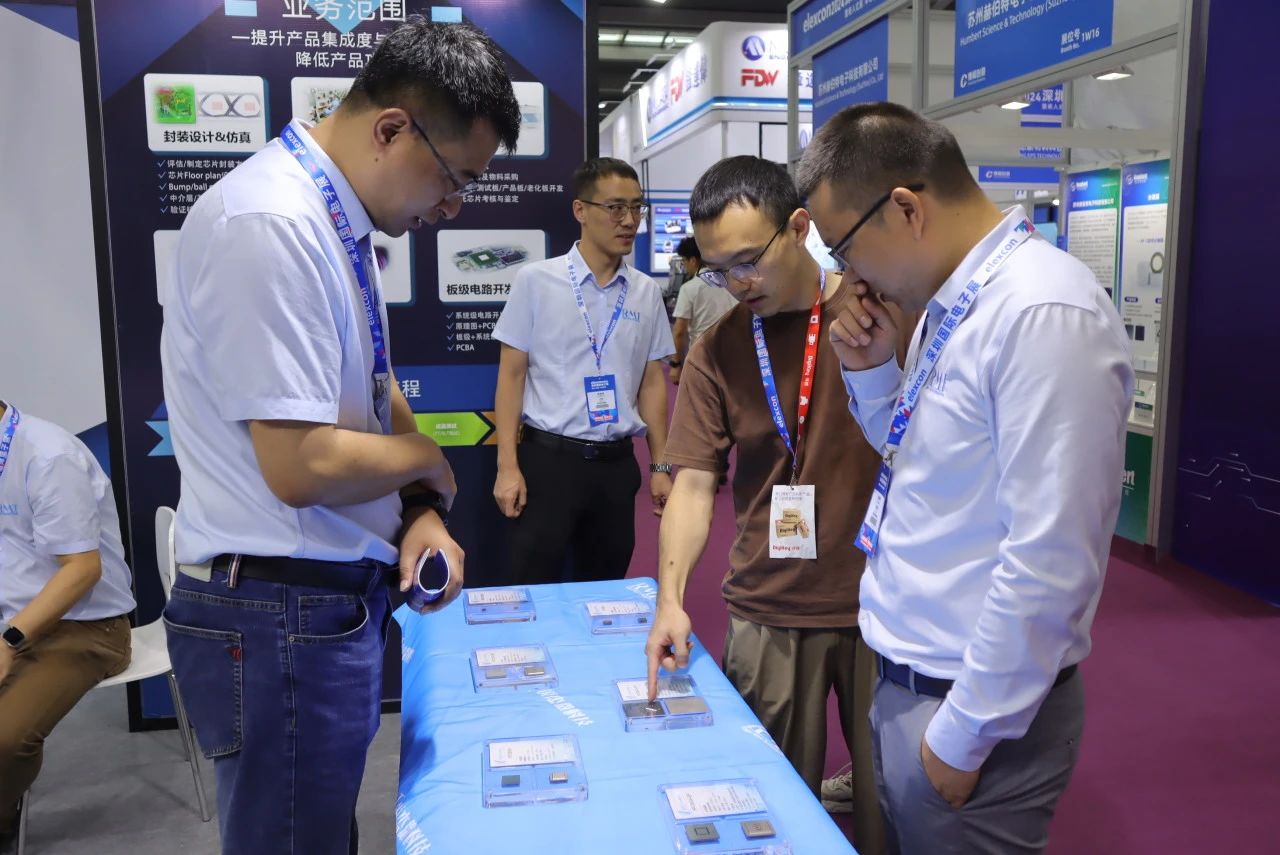

三天的展会中,锐杰微科技展位前始终人气爆棚、宾客云集。在本次展会上,锐杰微展示了多款FCBGA、HFCBGA-SiP等封装产品,并通过主题演讲、技术交流等多种方式,向到访观众及新老客户介绍锐杰微依托雄厚技术储备与产业布局、赋能大颗高算力芯片高端封测的综合实力。同时,锐杰微科技的销售、技术支持以及市场人员与前来咨询的业界人士,围绕锐杰微科技的两个全流程的Chiplet封装解决方案和项目合作等进行了广泛交流。

未来,锐杰微科技将继续致力于国产化先进工艺和高端芯片的研发任务,以丰富的案例经验、专业的技术研发团队,以及安全可靠的国产供应链资源,致力于为客户提供具有竞争力的全流程Chiplet封装技术解决方案,助力客户在激烈的市场竞争中保持优势。