锐杰微科技受邀出席2024晶上系统生态大会(SDSoW 2024)

AI赋能千行百业智能化是中国数字化转型发展的亮点,算力、算法和数据是AI技术发展的核心要素。算力需求推动了高端芯片持续发展,先进封装技术(Chiplet)迎来了难得发展机遇。锐杰微科技作为聚焦Chiplet&高端芯片的OSAT企业,荣幸受邀出席6月21日在国家会展中心(天津)举办的晶上系统生态大会(SDSoW 2024),首次担任SDSoW联盟常务理事单位,锐杰微科技-方家恩先生成功入选首届专家委委员。

方家恩先生在大会上阐述了Chiplet集成芯片的产业观点,围绕封装技术路线、芯粒互联的封装设计和组装工艺平台的重要节点,分享锐杰微在封装级的应用实践。

算力的旺盛需求带动高性能芯片市场持续增长

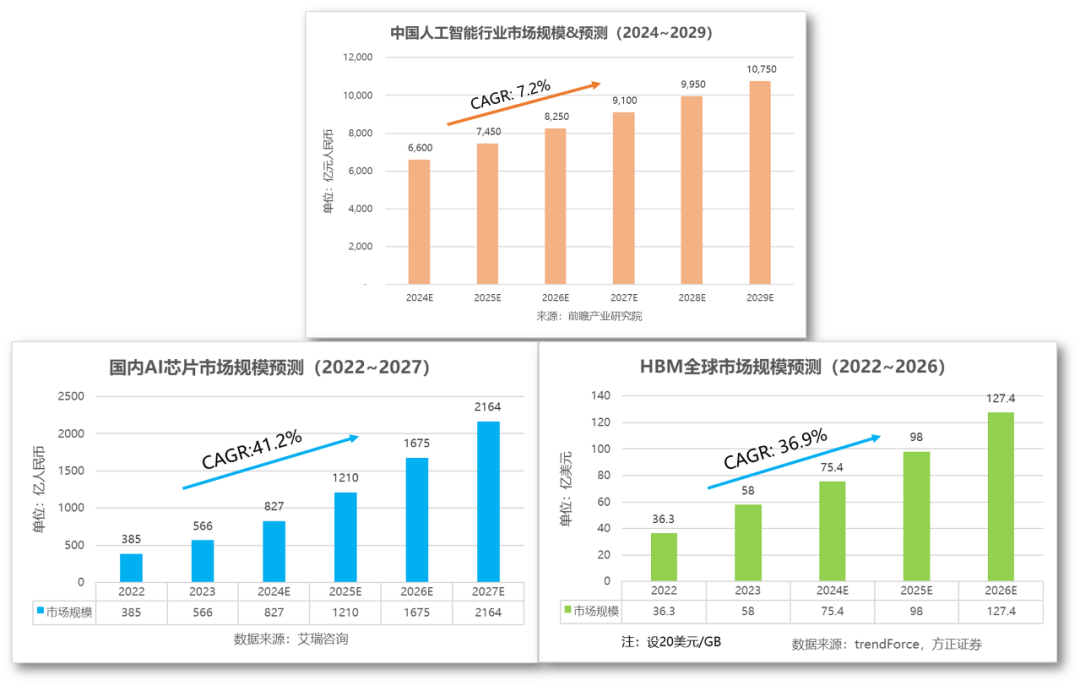

算力、算法和数据是推动人工智能发展的核心要素。根据分析机构预测:2024~2029年,中国人工智能市场规模,将从6600亿人民币达到近1.1万亿人民币,年复合增长率达到7.2%。2022~2027年,全球AI芯片市场规模,从319亿美元将达到1150亿美元,年复合增长率达到29.2%;HBM芯片市场规模,从36.3亿美元将达到127.4亿美元,年复合增长率达到36.9%。

高性能芯片广泛采用Chiplet技术已经成为趋势,成为推动算力发展的主流技术

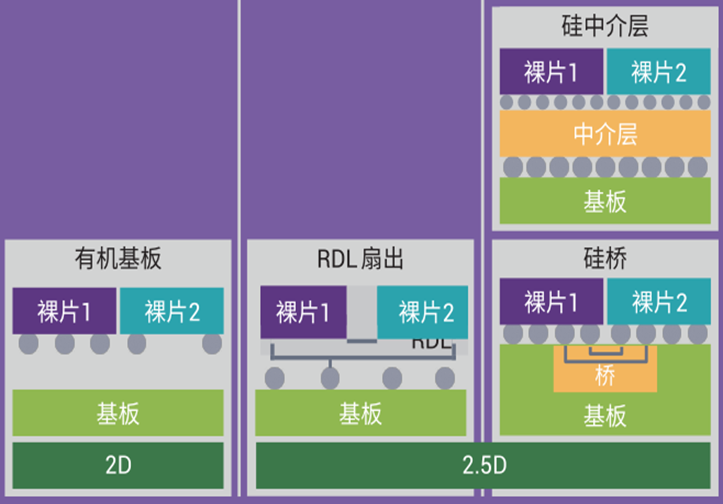

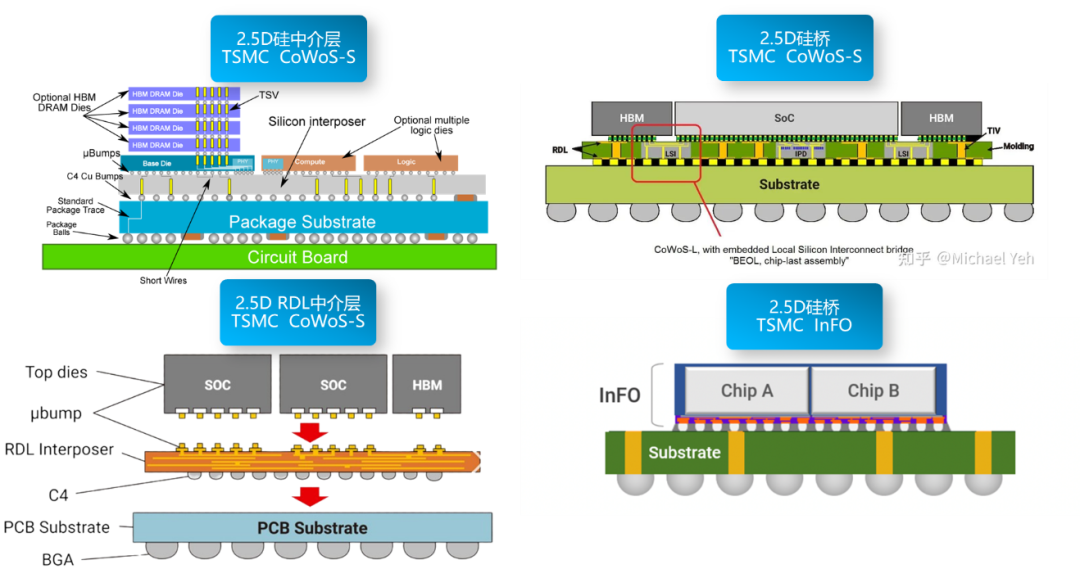

高算力、高带宽、低延时和低功耗/bit是高端芯片追求的关键技术指标。从近年全球头部芯片企业发布的高端芯片趋势看,如Nvidia(GB200,B200),AMD(MI300x),Intel(Intel Sapphire Rapids)等采用基于D2D互联的2.5D/3D先进封装形式。根据分析机构统计和预测,2023~2033年,Chiplet芯片市场规模,从3.1亿美元将达到107亿美元,年复合增长率达到42.5%。因此,Chiplet技术成为研究热点,发展前景广阔。

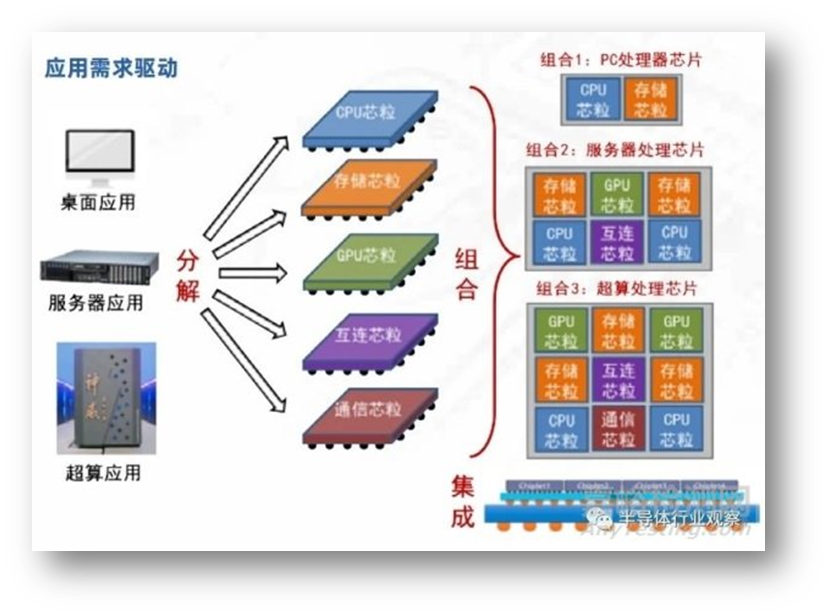

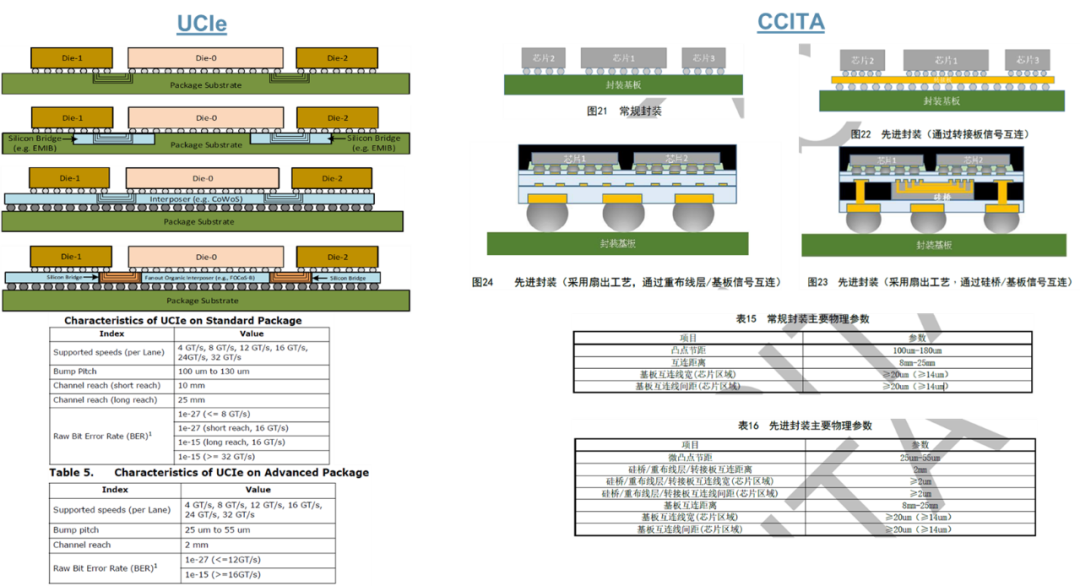

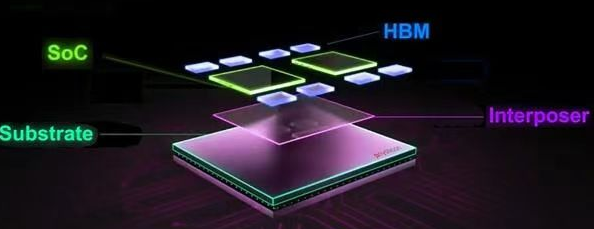

基于 Chiplet 技术的集成芯片是硅片级 IP 重构和复用的新架构。D2D 高速互联技术、面向设计和工艺全流程的封装工艺平台成为集成芯片发展的关键因素,Chiplet技术具有性能和工艺制程松耦合的特点,为IC开辟新的发展路径。

Chiplet 是一种把传统的单芯片设计方案改为基于多个芯粒进行设计,并利用先进封装工艺进行集成的芯片设计方法。Chiplet异质异构、跨尺度封装特点,在尺寸、功能密度、总功率/局部功率密度、IO数量/密度/速率、互联带宽/密度、热流密度、时延、单位bit功耗等关键指标具有显著提升空间,有效满足各类高算力应用场景。