2.5D封装应力翘曲设计

本文来自mediatek,发表于2023年。论文链接:https://ieeexplore.ieee.org/document/10195766。

主要内容:

本文通过测试、仿真分析了影响2.5D CoWoS翘曲、应力、可靠性的因素:real/dummyHBM、interposer 厚度、C4 bump高度。对2.5D package的设计非常有指导意义。

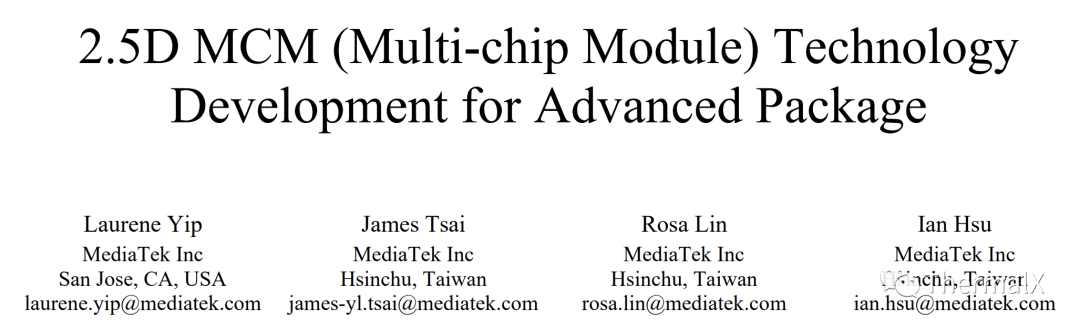

2.5D CoWoS封装结构示意图:

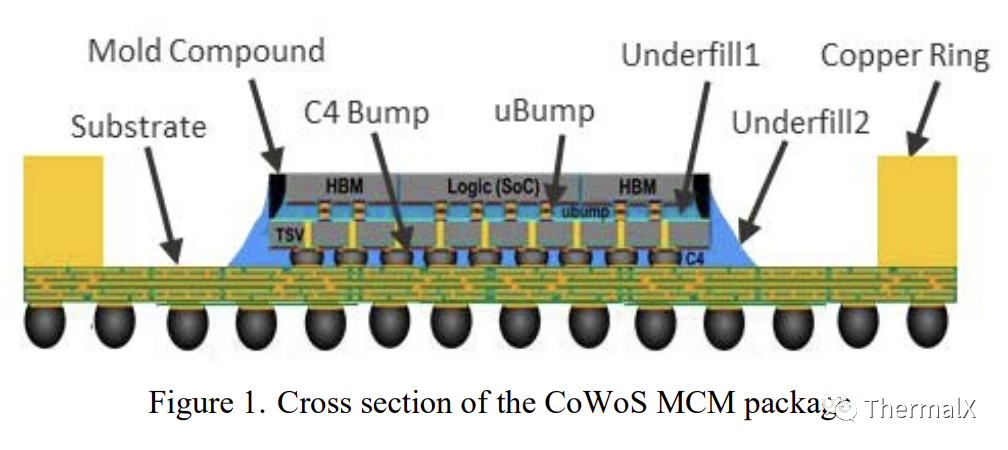

实物图:

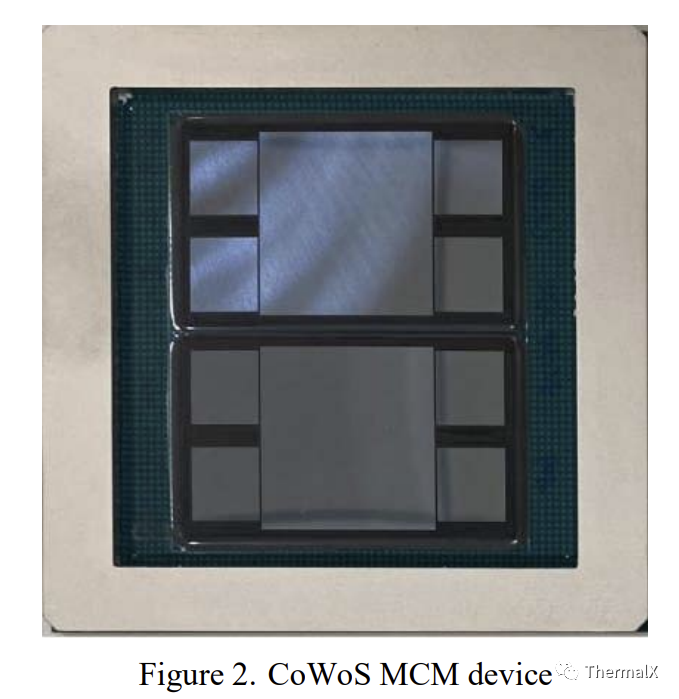

关键参数:

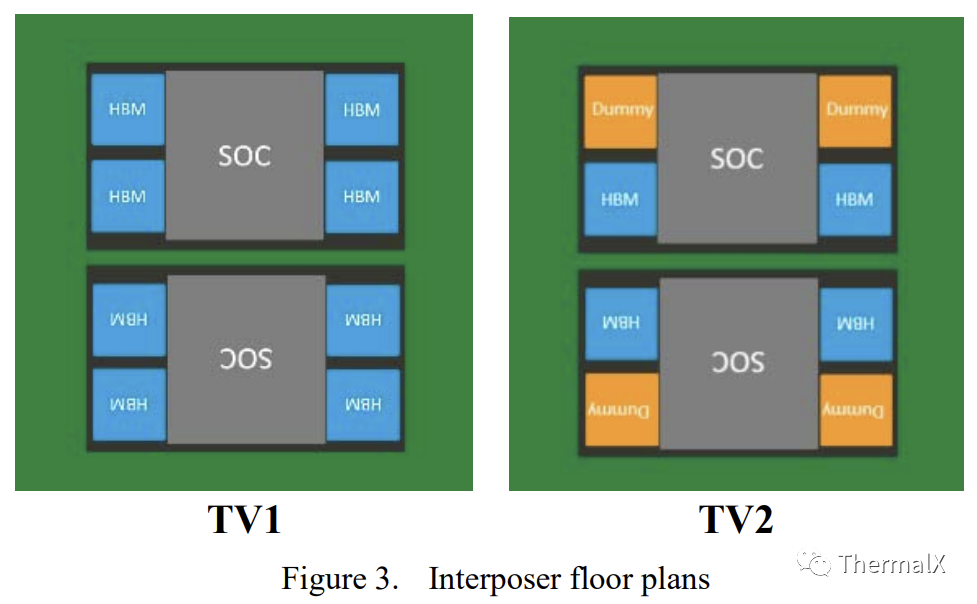

两种配置:

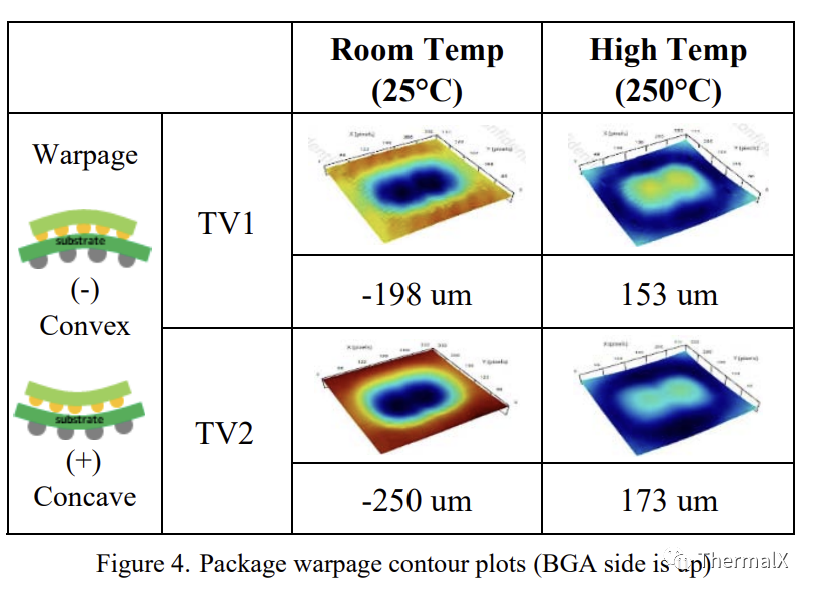

两种配置下reflow的翘曲测试结果:

由于结构的不对称,Dummy的要worse。不过按照JEDEC翘曲标准(140um、230um),貌似都fail了

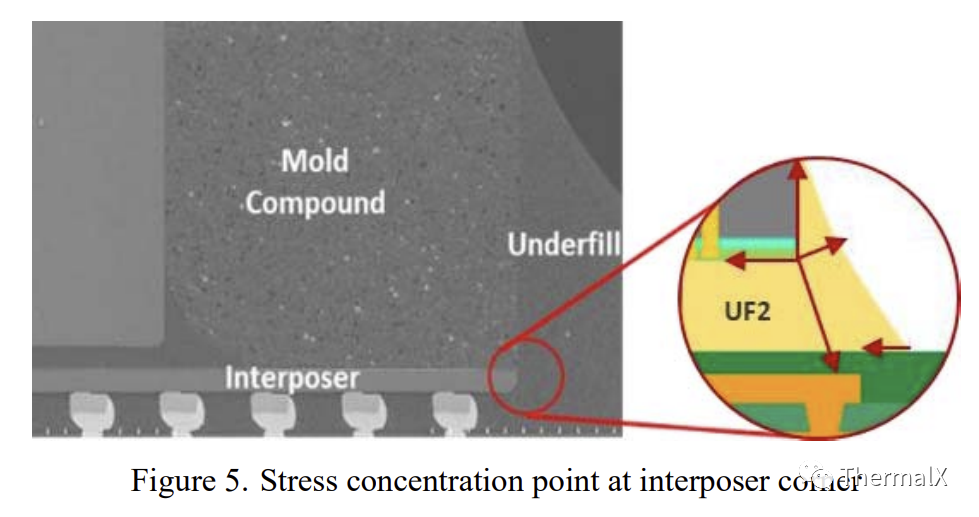

interposer边缘处是应力集中区域:

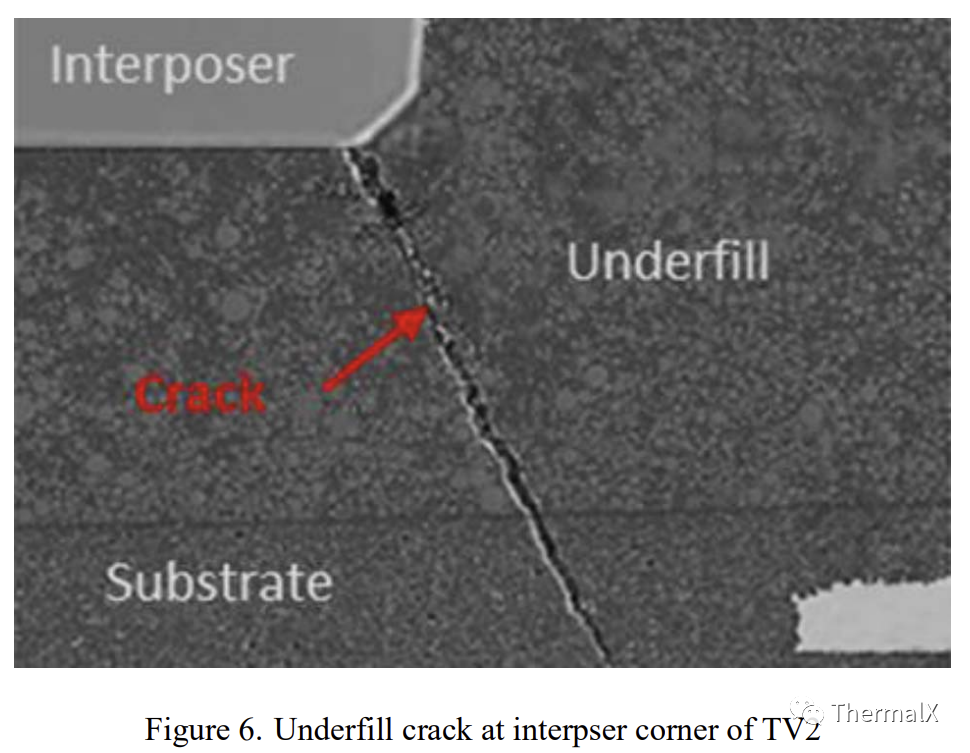

TCG(TC G类应力)200次测试后,TV1 OK,TV2 fail:

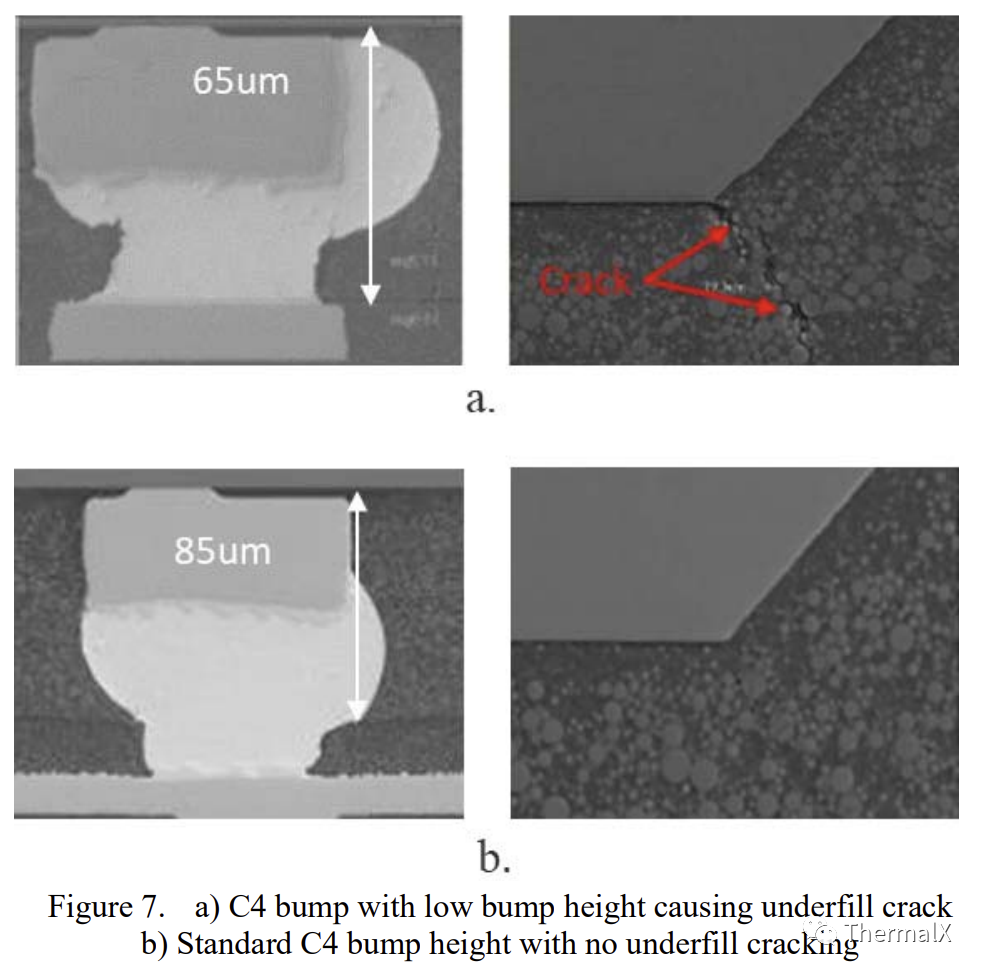

不同C4高度的影响:

65um C4 底填出现裂纹fail,85um C4 pass。

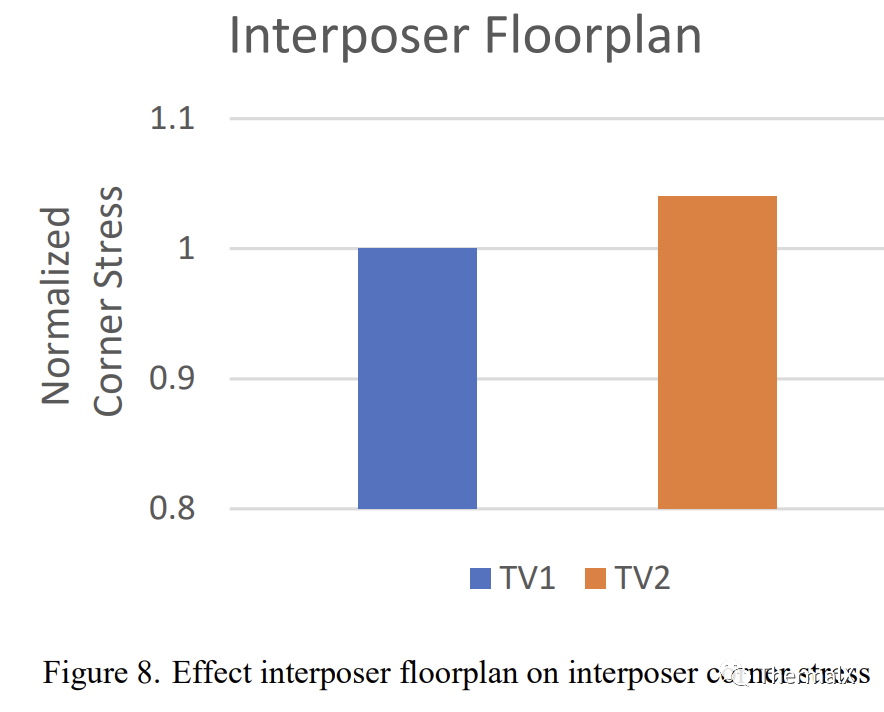

通过FEA进行分析TV1和TV2的interposer corner应力:

TV2比TV1高4%,因为HBM边缘处是Mold,与外面Mold的CTE mismatch没那么高。

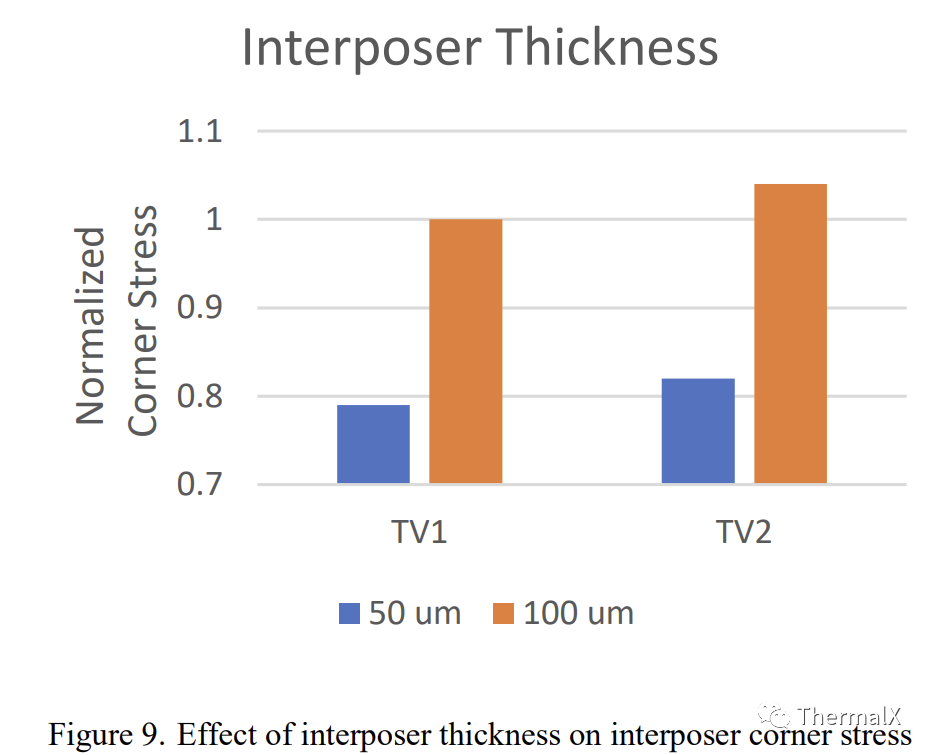

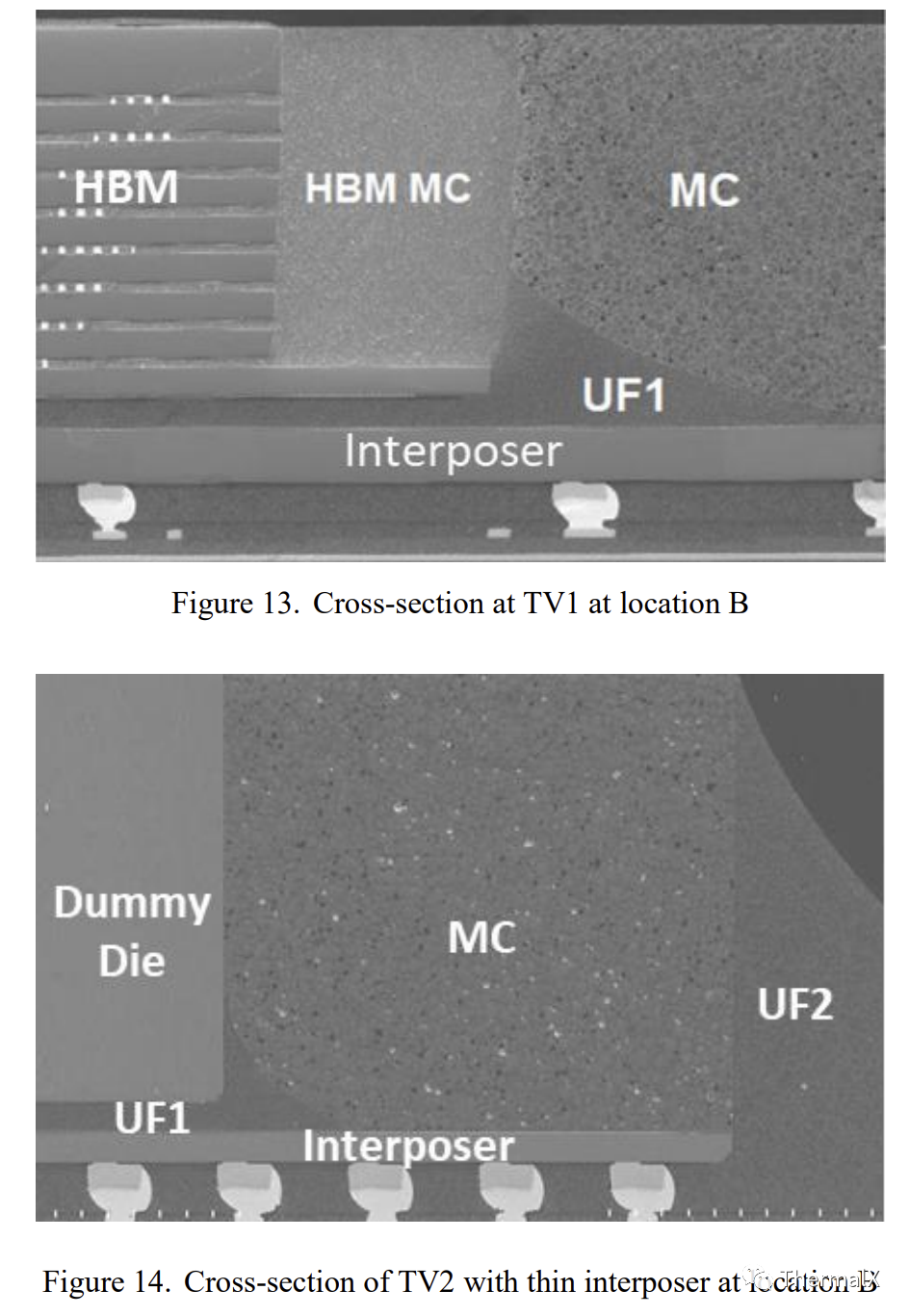

nterposer 50um厚会比100um的corner stress低:

因为interposer的CTE约4ppm/K,underfill的约为20ppm/K,基板的约为14ppm/K,interposer越薄,变形越小,TC循环时产生的应力也相对小。

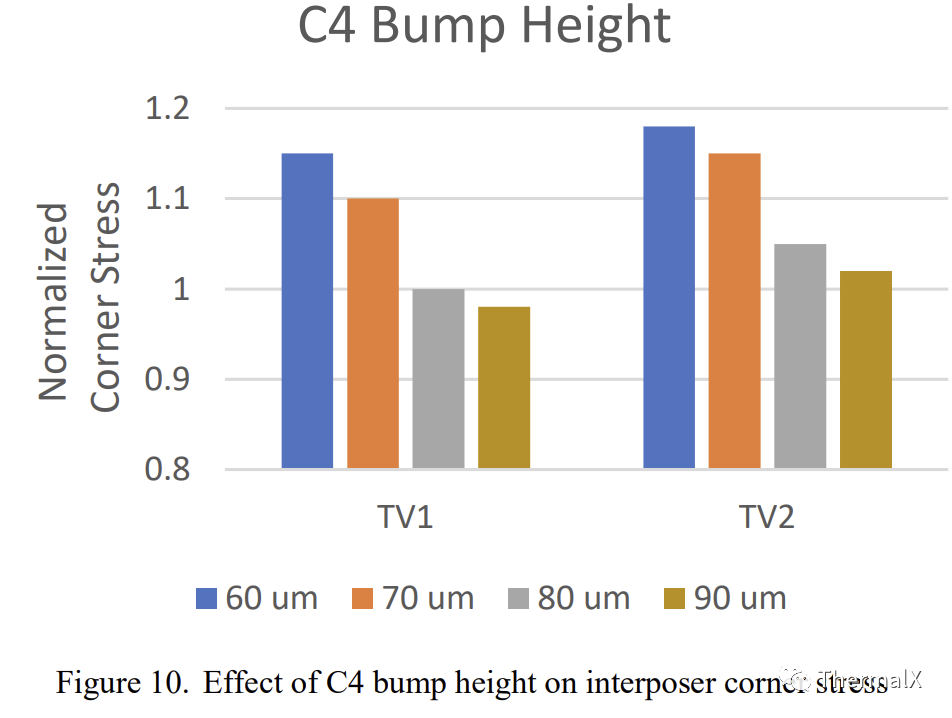

C4 越矮,interposer corner stress越大,因为C4越矮,边缘溢出的underfill2越多,应力越大。

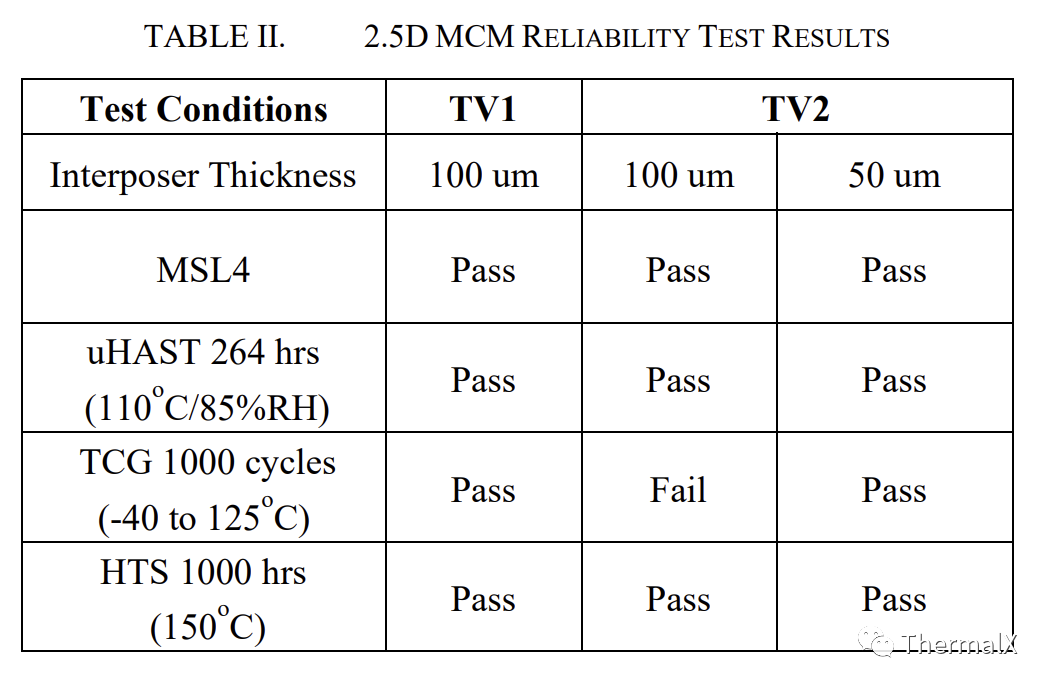

可靠性测试表明:

100um interposer的TV1和50um interposer的TV2均可pass。100um interposer的TV2则fail在了TCG测试,因为interposer corner应力集中产生了边缘区域的crack。

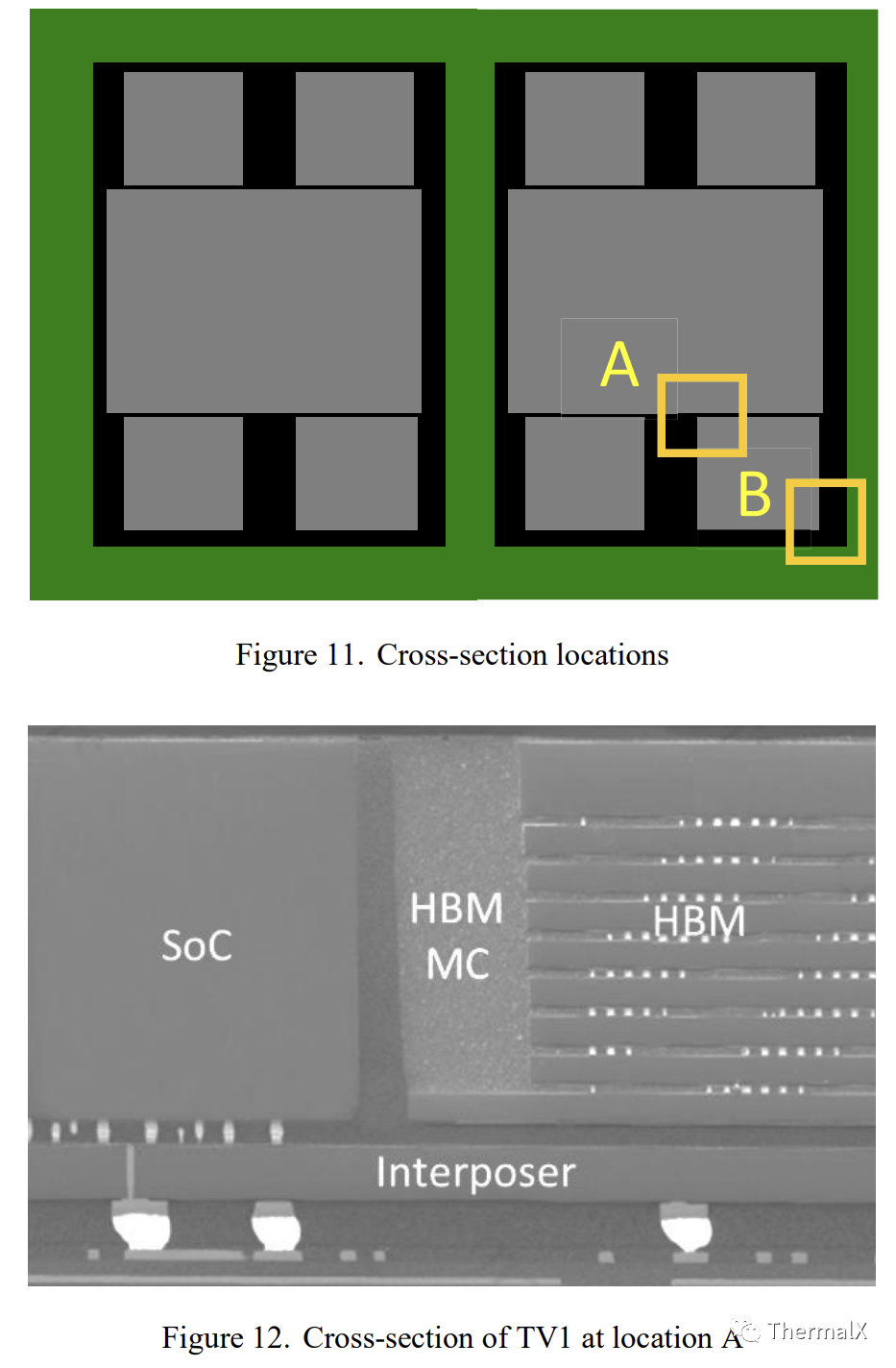

100um interposer TV1、50um interposer TV2局部图,都是OK的。

致谢:

作者致谢了mediatek的thermal团队、TSMC的仿真团队。

点评:

此研究对2.5D的设计非常有价值!