锐杰微科技@IIC Shanghai :全流程Chiplet封装技术解决方案助力大规模处理器发展

2024年3月28日,国际集成电路展览会暨研讨会(IIC)在上海盛大开幕。大会聚焦绿色能源生态发展、中国IC 设计创新、EDA/IP、MCU 技术与应用、高效电源管理及功率器件、Chiplet与先进封装技术、GPU/AI芯片与高性能计算应用等领域,涵盖高端峰会、技术论坛、产品和技术展示、企业新品发布等多维度活动内容。

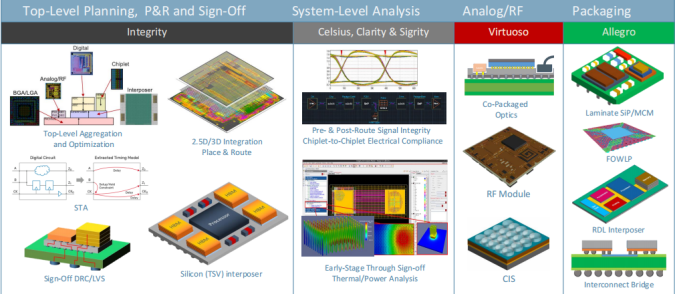

先进工艺芯片设计成本的飙升和摩尔定律接近物理极限的现实迫使半导体业界寻求现实可行的替代方案,以满足全球经济和新兴物联网及AI应用对半导体的持续需求增长。Chiplet 与先进封装的结合为业界带来了一线曙光。鉴于此,Chiplet与先进封装技术研讨会邀请专注于Chiplet前沿研究的学术界学者、EDA和IP厂商的技术专家,以及从事先进封装工艺开发的晶圆和封测厂商工程技术人员,一起探讨Chiplet设计、异构集成、Interposer工艺、EDA设计和仿真验证,以及HBM和接口标准等技术和应用难题及各种创新的解决方案。锐杰微科技董事长方家恩先生受邀参加,并发表《基于Chiplet芯片高速互联D2D的关键技术和应用》主题演讲。

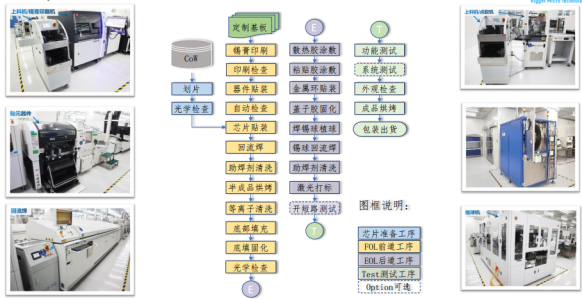

在谈到Chiplet关键工艺技术研究和封装能力建设方面,锐杰微已经在郑州基地搭建了Chiplet封装工艺试验床。开展关键工艺、材料试验和设计+工艺全流程的落地。在CoW工艺方面,已经制备了含有1.5倍光罩尺寸的硅中介板,die bump间距40um,bump数量达到20000个的集成组件。

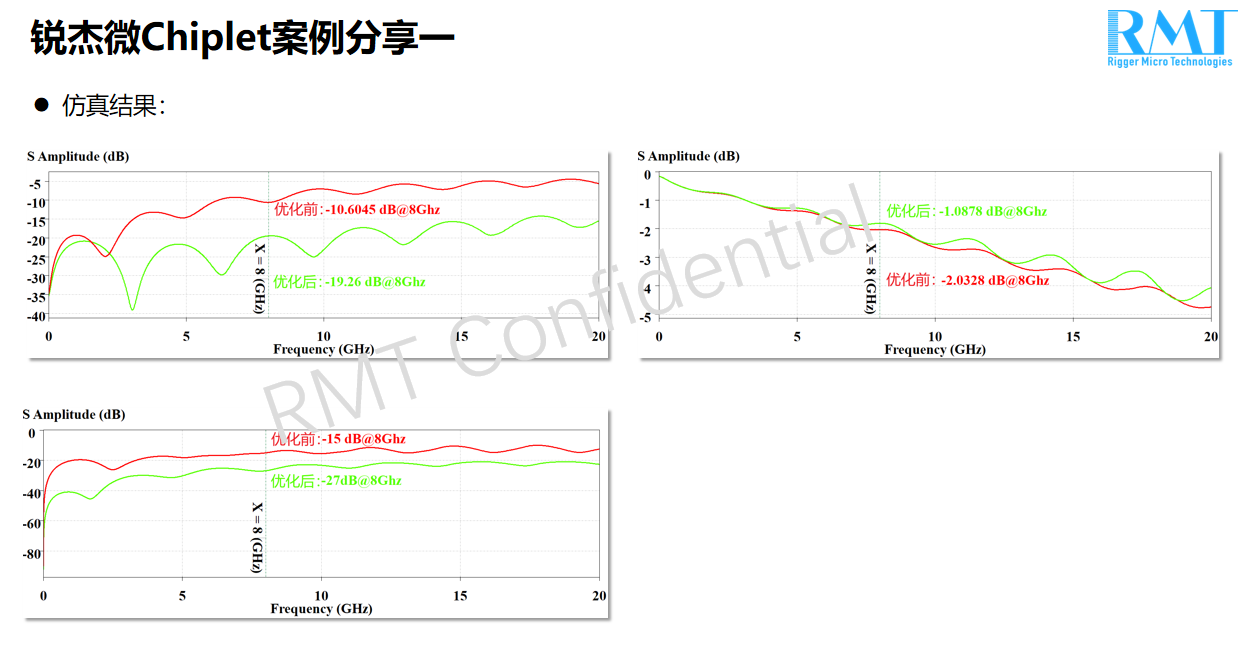

在Chiplet项目实践方面,已经成功交付16X 16Gbps带宽需求,基于2D封装平台,满足UCIe标准的IP验证芯片。目前已知行业内最早交付且同时能够满足UCIe Spec指标的方案,在产品集成度、成本、性能等方面有显著优势。在此基础上,正在评估32X 24Gbps带宽实现的可行性。

演讲最后,方家恩先生总结到,“锐杰微科技创立至今,一直瞄准国产化先进工艺及高端芯片的研发任务,公司配合行业一些新的技术做了很多积累。在大规模处理器方面,锐杰微具备丰富的案例经验、专业的技术研发团队,以及相对安全的国产供应链资源保障等优势,可以为客户提供更有竞争力的全流程Chiplet封装技术解决方案。”