精彩回顾《多元化需求驱动集成电路封装创新研究》

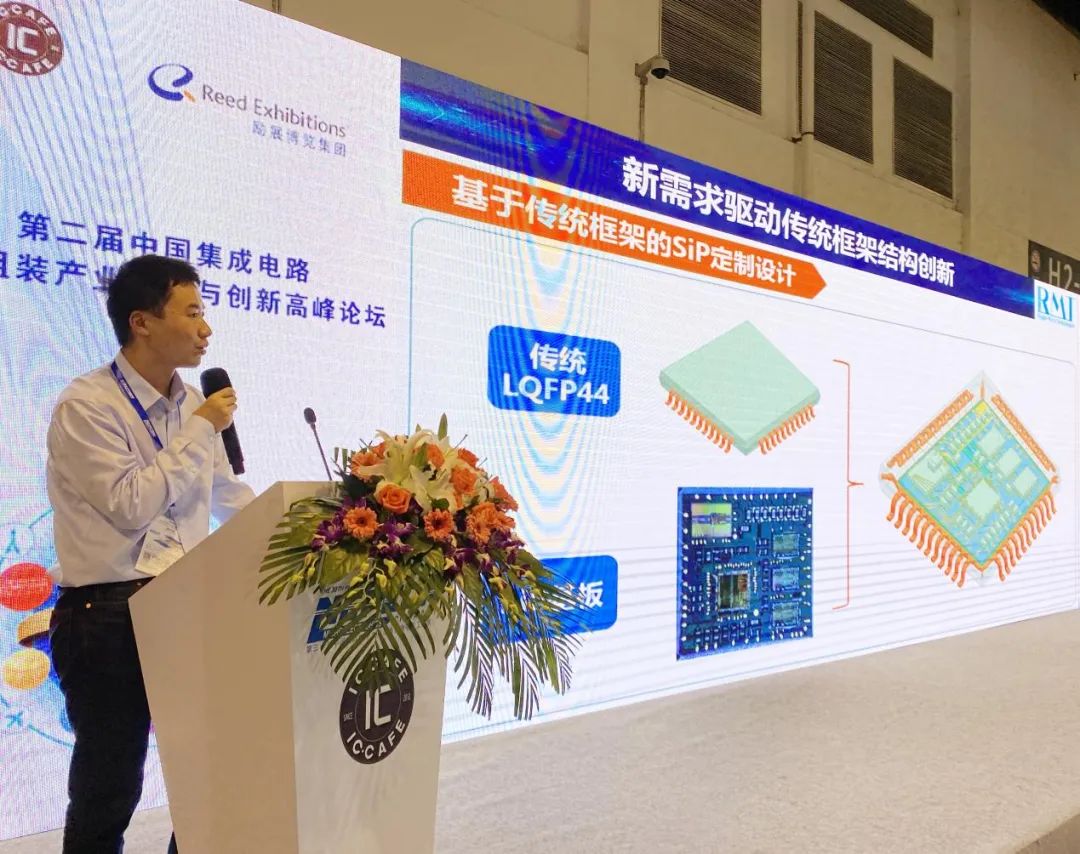

为期两天的“第二届中国集成电路暨微组装产业突围与创新高峰论坛”在上海世博展览馆2号馆于4月22日正式结束。会议以“芯”生态,新发展”为主题,在5G、AI、 IoT 时代下,从传统封装到先进封装,进行半导体封测环节涉及的技术或工艺问题探讨和交流,以及建立上下游产业链半导体关系网络圈。锐杰微同环旭、安靠、晶方、通富等一同受邀就本届论坛主题发表演讲。

2020年以来,突发性的新冠疫情给全球产业链带来巨大冲击,尤其在集成电路封测行业,产能爆满,基板供不应求,导致很多上游需求很难挤入各大OSAT(Outsourced Semiconductor Assembly and Testing/外包半导体(产品)封装和测试)封测厂,最新的产能交期基本延后到2023年左右。4月22日,高级研发总监彭一弘先生代表锐杰微科技参加2021年度微组装产业突围与创新高峰论坛,发表题为“多元化需求驱动集成电路封装创新研究” 主题演讲,阐述锐杰微在封装领域的创新和研究。

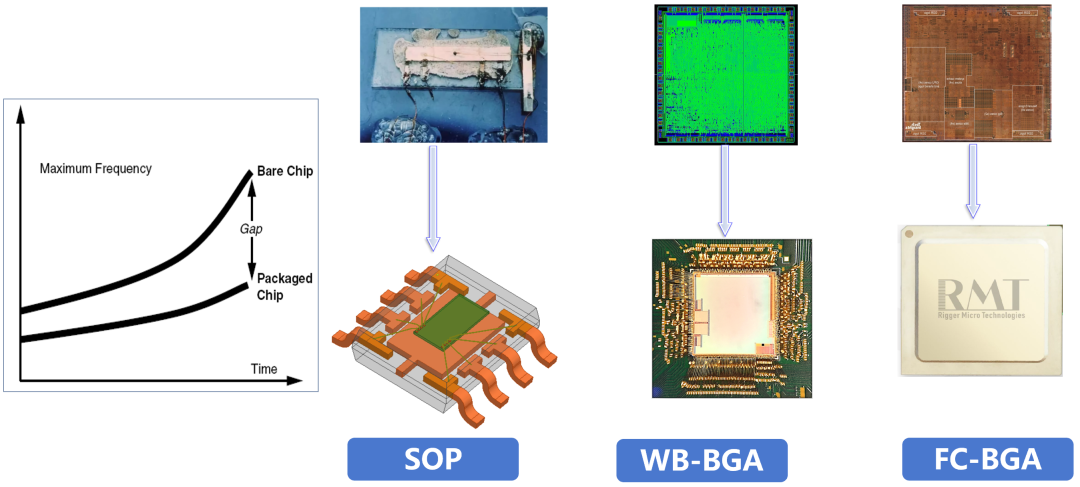

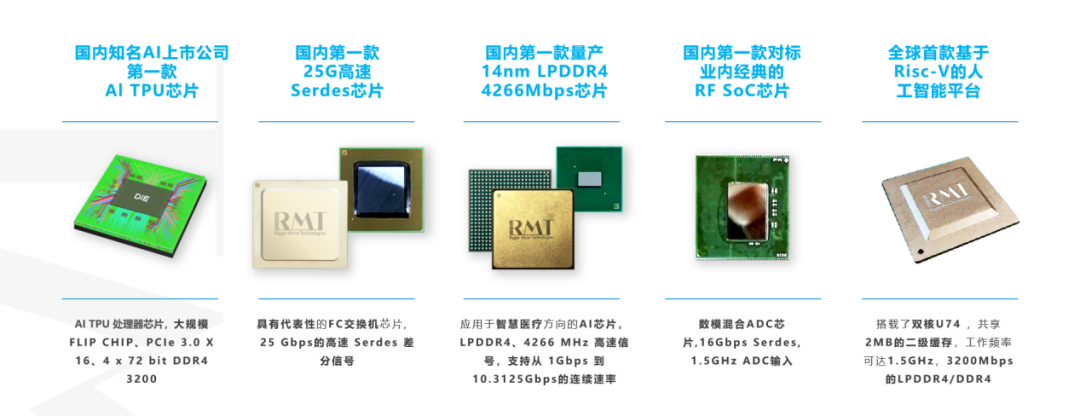

彭一弘总监首先阐述了整个集成电路发展的历史情况,以苹果A12 SoC(System on Chip/系统级芯片,也称片上系统)举例,采用7纳米工艺制程,单芯片中设计了包括逻辑处理单元、AI Machine Learning(人工智能的机器学习)单元、逻辑储存单元等大大小小接近30个功能处理模块,晶体管数量也从A11的43亿个爆涨到69亿个。随着集成电路封装技术的不断进步,封装后芯片与裸芯之间的性能差距也在不断缩小。同时,最新的封装技术也从传统的3D封装集成发展到3D硅集成。

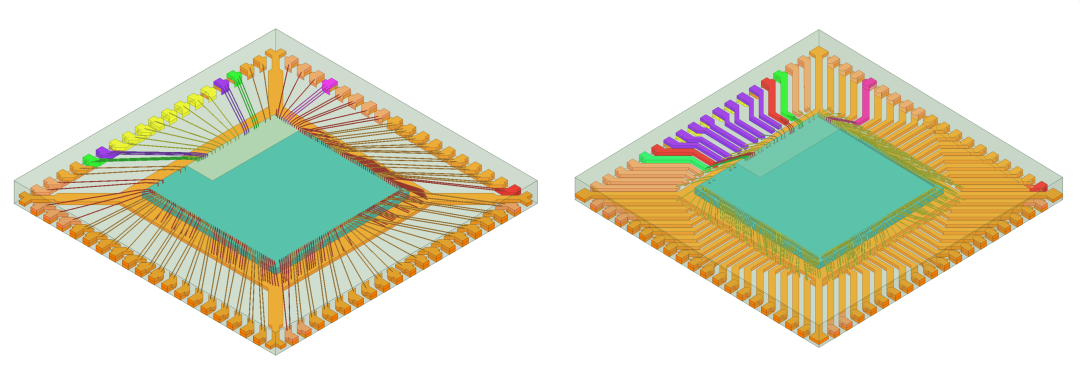

受惠于5G、AI 云端运算、大数据分析、高端服务器等应用需求,IC(Integrated Circuit/集成电路)封装基板持续处于产能紧缺且价格上扬的状态。部分FCBGA(Flip Chip Ball Grid Array/倒装芯片球栅格阵列)基板交期更是被拉长至45周以上。针对上述困难,在某些特殊的应用领域,锐杰微独辟蹊径,对传统引线框架进行优化定制,从原有的框架产品中加入全新的创新优化设计思路,让传统的LeadFrame封装形式能够实现更高的信号传输速率。在保障封装性能的同时,大幅降低了生产周期和生产成本。

最终芯片产品良率以及是否达到客户对于产品的预期,首要因素取决于前期封装设计的水平和整体方案的散热、EMI(Electro Magnetic Interference/电磁干扰)、SI(Signal Integrity/信号完整性)、PI(Power Integrity/电源完整性)、机械物理性能、材料流体方面的综合可靠性评估和方案优化能力。锐杰微致力探索电-热-力-磁等多个物理场下高性能核心控制芯片封装在设计、材料结构、制造工艺、测试验证等方面的加固优化技术,开发高安全性、高可靠性的封装产品。

彭一弘总监进一步阐述了现在电子产品逐渐趋于结构复杂化,功能多样化,类似移动终端、汽车领域、物联网、HPC(High Performance Computing/高性能计算)等。尤其在手机方面,10年前的手机普遍都是2G手机,使用到芯片的传输信号频段较少,信号传输速率也很低,相比现在的5G手机,用到很多个模块,大幅增加了封装难度,同时举例穿戴设备的智能手表,以前的手表只是机械式或是石英表,现在一个智能手表里集成有各种功能,类似血氧监测、心率监测等,里面会用到很多芯片,这样整个芯片模块的生产过程中对芯片的封装要求也会非常高。

最后,彭一弘总监阐述到,随着SoC工艺制程继续朝5nm、3nm、2nm甚至1nm推进,已经越来越逼近物理极限,实现难度也越来越高。通过把复杂SoC芯片拆解为标准化小芯片,利用先进封装技术来实现微系统的组合集成、3D集成或异构集成。从封装层面实现系统芯片化,从而实现多种电子元件的跨界集成、多种不兼容工艺整合重构、多种材料优化匹配、多种边界要求的结构设计。